## Soldering to a single atomic layer

Çağlar Ö. Girit<sup>a)</sup> and A. Zettl

Department of Physics, University of California, Berkeley, California 94720, USA and Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, California 94720, USA

(Received 24 August 2007; accepted 24 October 2007; published online 9 November 2007)

The standard technique to make electrical contact to nanostructures is electron beam lithography. This method has several drawbacks including complexity, cost, and sample contamination. We present a simple technique to cleanly solder submicron sized, Ohmic contacts to nanostructures. To demonstrate, we contact graphene, a single atomic layer of carbon, and investigate low- and high-bias electronic transport. We set lower bounds on the current carrying capacity of graphene. A simple model allows us to obtain device characteristics such as mobility, minimum conductance, and contact resistance. © 2007 American Institute of Physics. [DOI: 10.1063/1.2812571]

The conventional method of electrically contacting nanostructures is electron-beam lithography. While having good resolution, the procedure is complex, expensive, and time consuming. Moreover, the polymer resists and solvents used in the process leave residues that contaminate the sample or device. As a result, often the major contribution to the device resistance is not from the sample itself but from the contacts. Other lithography-free contacting techniques (such as shadow masks<sup>3</sup>) have been attempted, but they have their own drawbacks and have not been widely used. Here, we present an alternative method, effectively a miniaturization of soldering, which allows us to make submicron sized, Ohmic contacts to nanostructures of even single atom thickness. The technique is simple, inexpensive, rapid, and entirely avoids sample contamination.

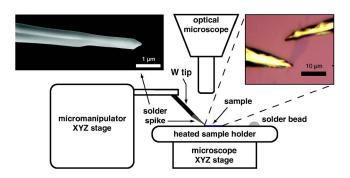

Figure 1 shows the main components of the nanosoldering setup: an optical microscope, a micromanipulator, and a heated sample holder. The sample to be contacted is placed on the holder along with a small bead of indium. The temperature of the holder is then raised to 170 °C, roughly 20 °C above indium's melting point. The room-temperature tungsten tip is inserted into the molten bead using the microscope and micromanipulator XYZ translation stages, and a spike of solder is slowly pulled out. Submicron spike tips [Fig. 1, scanning electron microscopy (SEM) image] are possible with careful adjustment of the temperature and pullout rate. The sample and spike tip are then successively positioned and aligned under the microscope using both XYZ stages. The microscope stage is then quickly raised, fusing the solder spike onto the sample as it comes into contact. Once all contacts are made, the sample heater is turned off and the contacts solidify to produce a device (Fig. 1, optical image).

Several low-temperature melting point alloys of indium and tin (Indalloy 1E, 4, 121, 182, 290) have also been used to make contacts. Indium is desirable because of its good adhesion to numerous surfaces, including silicon oxide. Flux and flux-bearing solders are avoided so as to keep the sample free from residues. In fact, flux as well as inert or forming gases which would normally be required to make a good bond, are unnecessary with this technique. Since the tungsten tip which draws out the solder spike is at room temperature,

oxidation of the solder spike is minimal.<sup>4</sup> Sample oxidation is also negligible for carbon nanostructures, since oxidation in air is significant only above 350 °C, <sup>5-7</sup> and for these materials, only solders with eutectic or melting points in the range of 118–280 °C are used. Ultimately, once the procedure is fine tuned, the nanosolder contacts are extremely reliable.

Using this technique, we contacted graphene, single sheets of graphite which are extracted by micromechanical exfoliation. This material has garnered much attention due to interesting physics and promise for applications. Single sheet samples are identified optically by contrast analysis and confirmed by the existence of a sole peak near 2700 cm<sup>-1</sup> in their Raman spectrum. Once a suitable sample is isolated, contacts can be soldered to produce a working device within minutes. A typical optical image of a nanosolder contacted graphene device with two terminals is shown in Fig. 1. Samples are usually 10–20  $\mu$ m in size, with contact separations typically several microns.

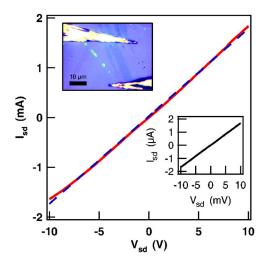

Figure 2 shows the source-drain current  $I_{\rm sd}$  of a nanosoldered graphene device measured as a function of applied voltage  $V_{\rm sd}$  in the range of  $\pm 10$  V at room temperature in ambient conditions. The IV characteristic is linear even up to such high source-drain voltages. The resistance of the device, from the linear fit (dashed line), is 5.7 k $\Omega$ . The inset, an IV trace taken in the range  $V_{\rm sd}$ = $\pm 10$  mV, gives a low-bias resistance of 6.0 k $\Omega$ , differing by 5% despite the 1000 times

FIG. 1. (Color online) Schematic of the nanosoldering setup, consisting of an optical microscope, micromanipulator, and sample heater, used to contact graphene and other nanostructures. Upper left: scanning electron microscope image of an indium solder spike ending in a 50 nm radius tip (scale bar, 1  $\mu$ m). Upper right: optical microscope image of a contacted graphene device (scale bar, 10  $\mu$ m).

a)Electronic mail: cog@berkeley.edu

FIG. 2. (Color online) Source-drain current-voltage characteristic, with source-drain voltage  $V_{\rm sd}$  in the range of ±10 V, of the solder contacted graphene device shown in the inset, optical image (scale bar 10 μm, image contrast enhanced). Dashed line is linear fit to resistance 5.7 kΩ. Inset plot is low-bias *I-V* curve of same device, with a resistance of 6.0 kΩ. The back-gate voltage  $V_{\rm bg}$ =0 V.

smaller range in  $V_{\rm sd}$ . Taking the device geometry into account, a lower bound on the current carrying capacity of single layer graphene in air on a silicon oxide substrate can be placed at 390 A/m (where per meter refers to the sheet width) or 120 MA/cm<sup>2</sup> bulk assuming a sheet thickness of 3.35 Å, the graphite interlayer spacing. This bulk current carrying capacity is more than 1000 times that of a superconductor.<sup>17</sup> Since our value is a lower bound, it is quite probable that the actual limit is comparable to that of multiwall carbon nanotubes, <sup>18</sup> roughly 10<sup>9</sup> A/cm<sup>2</sup>. In vacuum (10<sup>-5</sup> mbar), we have observed current densities in graphene as high as 500 A/m without device failure. Assuming uniform power dissipation, the power density of the device in Fig. 2 is 16 kW/cm<sup>2</sup>, more than two orders of magnitude larger than the present processor heat flux. 19 With such high current carrying capacities and power densities, graphene electronics as envisaged, for example, by Berger et al., 14 are expected to operate reliably at far higher power levels than possible for conventional Si-based devices.

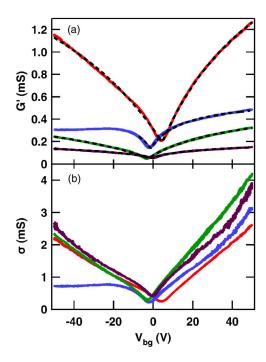

Figure 3(a) shows the two-terminal conductances G' of four soldered graphene devices as a function of back-gate voltage  $V_{\rm bg}$  at room-temperature in vacuum. All graphene samples, identically prepared and solder contacted are remarkable in that their Dirac points  $V_D$ —the location of the conduction minimum—are within 5 V of  $V_{\rm bg}$ =0 V without any annealing or processing. This is in contrast with the literature of electron-beam lithographed devices,  $^{20}$  where  $V_D$  in the tens of volts is common. The clean, solder-contacted samples, without lithography residues to charge the sample and shift the Dirac point away from zero, are at least neutral, if not undoped. This is an important indication of how processing parameters influence the device characteristics.

Although these are two terminal measurements, we can nevertheless estimate the effective, or device, mobility, the minimum conductivity, and the contact resistance with a simple model. We relate the Drude equation for conductivity,  $\sigma = en\mu$ , with n as the carrier density and  $\mu$  as the mobility, to the conductance using  $\sigma = GL/W$ . The experimentally measured conductance G' includes the contact resistance  $R_c$  via  $1/G' = R_c + 1/G$ . For graphene in a standard transistor

FIG. 3. (Color online) (a) Two-terminal conductance G' of four solder-contacted graphene devices measured as a function of back-gate voltage  $V_{\rm bg}$ . The dashed black lines are fits to the data with a Drude model modified to account for the electric field effect and the contact resistance. (b) Intrinsic sheet conductivities for the same devices obtained by subtracting the contact resistance as determined from the fits and accounting for the device aspect ratios. Gate voltage is swept both ways, showing negligible hysteresis.

geometry, the carrier density depends on the back-gate voltage as  $n=c'|V_{\rm bg}-V_D|/e$ , where the specific capacitance c' for a 300 nm silicon oxide gate thickness is 115 aF/ $\mu$ m<sup>2</sup>. Finally, we add a phenomenological parameter  $\sigma_D$  to account for the nonzero minimum conductance and allow differing electron and hole mobilities  $\mu_e$  and  $\mu_h$  to obtain

$$\frac{1}{G'} = R_c + \frac{L/W}{c' \mu_{e,h} |V_{\text{bg}} - V_D| + \sigma_D},\tag{1}$$

using  $\mu_e$  for back-gate voltage  $V_{\rm bg} \!\! > \!\! V_D$  and  $\mu_h$  in the range  $V_{\rm bg} \!\! < \!\! V_D$ . The aspect ratio, L/W, is determined from optical images of the devices. In general, this model will overestimate the contact resistance as any intrinsic sublinearity in the conductance-gate voltage curves will contribute to  $R_c$ . While the data can be fitted to more fundamental theories, the simple model suffices here to characterize the graphene devices.

Figure 3(b) plots the intrinsic device conductivity,  $\sigma = L/W(1/G \cdot -R_c)$ , as a function of applied back-gate voltage  $V_{\rm bg}$ , where the contact resistance  $R_c$  is extracted from the fits [Fig. 3(a), dashed black lines]. The conductivity curves are relatively linear for almost all the devices, indicating the fit is good. Note that it is clear from the plots that the mobilities (slopes of the curves) and minimal conductivities are roughly the same for all devices. The electron mobilities range from 4500 to 6200 cm<sup>2</sup>/V s and hole mobilities range from 3000 to 3600 cm<sup>2</sup>/V s, show much less variation than, in electron-beam lithography defined devices.<sup>20</sup> The minimal conductivities are 210, 230, 300, and 440  $\mu$ S. The contact resistance per lead over nine devices varied from 190 to 1700  $\Omega$ , with a mean of 680  $\Omega$  and a standard deviation of 450  $\Omega$ , comparable to the best electron-lithography fabricated devices.

The solder contact method can also be used to contact nanotubes and nanowires. We have used SEM to locate multiwall carbon nanotubes relative to predefined optically visible markers. The soldering technique, as described above, can then be used by positioning the leads relative to the markers. However, a better method would be to use a piezomicromanipulator inside the SEM itself, along with a heated sample stage, and solder the contacts in situ. Other applications of the solder technique are wirebonding and shadow mask alignment. To wirebond devices which already have leads, fine wire is placed near the leads and then a solder spike is deposited, with the sample stage hot, over both lead and wire. When the heater is turned off, the solidified spike fixes the wire to the substrate and provides electrical contact to the lead. The wirebonding and sample soldering can also be performed in a single step, with the solder spike both contacting the sample and fixing the wire. To align shadow masks, a similar process is used. The mask is placed on top of the substrate, over the sample, and soldered at the corners. The micromanipulator is then used to push the mask into alignment, and the heater is turned off to fix the mask.

Solder contacts are a simple, efficient means of producing functional nanostructure devices based on graphene, nanotubes, or other materials. Not only the contacts are Ohmic, but also the resultant devices are clean and the device characteristics are consistent. The contacts, capable of sustaining large currents without failure, allow for investigation of high-bias electronic transport properties.

We thank A. Kis and R.-E. Chee for assistance with experiments, Y. Zhang and Y.-W. Son for helpful discussions, and B. Kessler for supplying the nanotube samples. Ç.Ö.G. acknowledges support through a National Science Foundation Graduate Research Fellowship. A.Z. acknowledges support from the Miller Institute for Basic Research in Science. This work was supported in part by the Director, Office of Energy Research, Office of Basic Energy Sciences, Division of Materials Sciences, of the U.S. Department of Energy under Contract No. DE-AC03-7600098.

- <sup>1</sup>P. Rai-Choudhury, *Handbook of Microlithography, Micromachining, and Microfabrication* (SPIE, Bellingham, WA, 1997), Vol. 1, p. 139.

- <sup>2</sup>E. Stern, G. Cheng, J. F. Klemic, E. Broomfield, D. Turner-Evans, C. Li, C. Zhou, and M. A. Reed, J. Vac. Sci. Technol. B **24**, 231 (2006).

- <sup>3</sup>N. Staley, H. Wang, C. Puls, J. Forster, T. N. Jackson, K. McCarthy, B. Clouser, and Y. Liu, Appl. Phys. Lett. **90**, 143518 (2007).

- <sup>4</sup>H. Schoeller, J. Kim, S. Park, and J. Cho, in *Advanced Electronic Packaging*, MRS Symposia Proceedings No. 968, edited by V. P. Atluri, S. Sharan, C. P. Wong, and D. Frear (Materials Research Society, Pittsburg, 2007), pp. V03–07.

- <sup>5</sup>B. T. Kelly, B. J. Marsden, K. Hall, D. G. Martin, A. Harper, and A. Blanchard, IAEA-TECDOC-1154, 2000 (unpublished).

- <sup>6</sup>W. Jiang, G. Nadeau, K. Zaghib, and K. Kinoshita, Thermochim. Acta 351, 85 (2000).

- <sup>7</sup>X. H. Chen, C. S. Chen, Q. Chen, F. Q. Cheng, G. Zhang, and Z. Z. Chen, Mater. Lett. **57**, 734 (2002).

- <sup>8</sup>A. K. Geim and K. S. Novoselov, Nat. Mater. **6**, 183 (2007).

- <sup>9</sup>K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, Science **306**, 666 (2004).

- <sup>10</sup>K. S. Novoselov, D. Jiang, F. Schedin, T. J. Booth, V. V. Khotkevich, S. V. Morozov, and A. K. Geim, Proc. Natl. Acad. Sci. U.S.A. **102**, 10451 (2005)

- <sup>11</sup>Y. B. Zhang, Y. W. Tan, H. L. Stormer, and P. Kim, Nature (London) 438, 201 (2005).

- <sup>12</sup>K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, M. I. Katsnelson, I. V. Grigorieva, S. V. Dubonos, and A. A. Firsov, Nature (London) 438, 197 (2005).

- <sup>13</sup>J. C. Meyer, A. K. Geim, M. I. Katsnelson, K. S. Novoselov, T. J. Booth, and S. Roth, Nature (London) 446, 60 (2007).

- <sup>14</sup>C. Berger, Z. M. Song, X. B. Li, X. S. Wu, N. Brown, C. Naud, D. Mayo, T. B. Li, J. Hass, A. N. Marchenkov, E. H. Conrad, P. N. First, and W. A. de Heer, Science 312, 1191 (2006).

- <sup>15</sup>Z. H. Ni, H. M. Wang, J. Kasim, H. M. Fan, T. Yu, Y. H. Wu, Y. P. Feng, and Z. X. Shen, Arch. Hist. Exact Sci. 7, 2758 (2007).

- <sup>16</sup>A. C. Ferrari, J. C. Meyer, V. Scardaci, C. Casiraghi, M. Lazzeri, F. Mauri, S. Piscanec, D. Jiang, K. S. Novoselov, S. Roth, and A. K. Geim, Phys. Rev. Lett. 97, 187401 (2006).

- <sup>17</sup>S. Frank, P. Poncharal, Z. L. Wang, and W. A. de Heer, Science **280**, 1744 (1998).

- <sup>18</sup>B. Q. Wei, R. Vajtai, and P. M. Ajayan, Appl. Phys. Lett. **79**, 1172 (2001).

<sup>19</sup>M. J. Ellsworth, ITHERM '04-The Ninth Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, 2004 (unpublished), Vol. 2.

- <sup>20</sup>Y.-W. Tan, Y. Zhang, K. Bolotin, Y. Zhao, S. Adam, E. H. Hwang, S. D. Sarma, H. L. Stormer, and P. Kim, arXiv:0707.1807.

- <sup>21</sup>E. H. Hwang, S. Adam, and S. D. Sarma, Phys. Rev. Lett. **98**, 186806 (2007).

- <sup>22</sup>S. Adam, E. H. Hwang, V. M. Galitski, and S. D. Sarma, arXiv:0705.1540.

<sup>23</sup>F. Schedin, A. K. Geim, S. V. Morozov, E. W. Hill, P. Blake, M. I. Katsnelson, and K. S. Novoselov, Nat. Mater. 6, 652 (2007).